3. MCU 보드 제작기 - 파워 블록(LDO Regulator)

저번 글에서 다이오드 OR회로를 이용하여 여러 외부 전원 사이의 쇼트와 역방향 전류를 방지해 주었다. 이제는 MCU 보드를 동작시키는데 적압한 전압을 가지는 전원으로 전압 레벨을 조정해주어야한다. LDO Regulator를 사용하면 쉽게 원하는 전압 레벨로 전원을 조정할 수 있다. LDO Regulator는 전압 레귤레이터의 일종으로, 전압을 안정화 시키는 역할을 한다. LDO는 Low Dropout의 약자로 LDO Regulator는 낮은 입출력 전위차에서도 동작하는 리니어 레귤레이터를 뜻한다. LDO의 원리는 OPAMP와 증폭기(BJT, FET 등)를 이용하여 feedback 회로를 구성하고 출력 전압을 사용자가 원하는 전압의 전원으로 출력하는 것이다. 자세한 내용은 이 블로그의 글을 참고하기를 바란다.

#20. LDO(Low Drop-Out) Regulator 동작 원리 이해하기

회로설계에 있어 전원부 회로는 가장 기본이자 필수입니다. 외부 전원을 입력받아 원하는 전압 레벨을 만들기 위해 스위칭 Regulator를 사용하거나 때에 따라 LDO를 사용하기도 합니다. 효율이 중

analog-circuit-design.tistory.com

OR 회로를 거친 전원은 대략적으로 5V의 전원이 5V - 0.35V인 4.65V 정도로 강하가 이루어진다. 우리의 목표는 4.65V 전원을 3.3V 전원으로 바꾸어주는 것이다. 회로 설계의 목표는 다음과 같다.

- 출력 전압 : 3.3V(고정형 - 가격이 싸다)

- 출력 전류 : 300mA 이상 (선정 이유는 쇼트키 다이오드를 선정했을 때와 같다. MCU 최대 소모 전류 x 2)

- Dropout 전압 : 목표인 3.3V 보다 최소로 커야하는 전압의 크기, Vdrop < 1.35V

- 시스템 안정성 : 5V보다 큰 전압의 전원이 인가되었을 때(+60%), 작은 전압의 전원이 인가되었을 때(-30%), RF 전자기장 노이즈가 발생하였을 때를 고려한다.

LDO Regulator 데이터시트에서 제공하는 응용 예시를 참고하겠다.

입력과 출력에 각각 1uF 이상의 커패시터를 병렬로 연결할 것을 권하고 있다. 해당 커패시터는 교류 성분의 노이즈를 제거해주는 역할을 하거나 전원에서 발생하는 리플(Ripple)을 평탄화하는 역할을 한다. 사실 예시의 회로를 사용하여도 동작에는 큰 문제가 없다. 그러나 보다 안정적인 회로를 위해 추가적인 설계를 진행해 보자.

LDO Regulator는 LP5907MFX-3.3/NOPB를 선택하였다. 3.3V 고정형 LDO 레귤레이터이고, 최대 출력 전류 250mA, Dropout 전압 0.2V ~ 0.25V, SOT-23-5 패키지이다. 기준인 300mA 보다는 작지만 재고량 등을 고려하여 유연하게 선택하였다. JLCPCB 번호는 C80670이다.

https://jlcpcb.com/partdetail/TexasInstruments-LP5907MFX_3_3NOPB/C80670

LP5907MFX-3.3/NOPB | Texas Instruments | Voltage Regulators - Linear, Low Drop Out (LDO) Regulators | JLCPCB

One-Stop Turnkey PCBA & Free Asembly for Your PCBs Get $30 New User Coupons & Monthly $24 PCBA Coupons

jlcpcb.com

1. 언더슈트 30% 대응

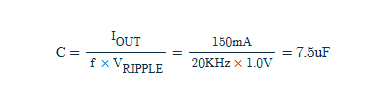

회로의 공진 주파수를 알기는 어려우니 20kHz 이상의 정현파에 대한 링잉을 가정하고 링잉 수식에 적용하여 적정 커패시터 용량을 산출해보자. 수식 적용이 가능한 이유는 평활 회로가 장착되어 있기 때문이다. (자세한 내용은 규칙으로 배우는 임베디드 시스템 - 484pg를 참고하면 된다. 기회가 되면 해당 주제에 대해서 다루겠다.)

7.5uF보다 마진을 두어 10uF 탄탈커패시터를 쓰기로 하였다. 탄탈커패시터는 상대적으로 안정적인 고주파수 응답 특성을 가지고 있어서 링잉 제거를 목적으로 적합하다. 커패시터 종류에 대해서는 다음 블로그의 글을 참고하면 좋을 것 같다.

#19. 커패시터(Capacitor)의 종류

회로의 수동소자 R(Resistor), L(Inductor), C(Capacitor) 중 중요한 한 축을 담당하는 커패시터의 종류에 대해 설명하려고 합니다. 커패시터의 사용 용도가 다양하기 때문에 그 용도에 맞는 커패시터들이

analog-circuit-design.tistory.com

내가 선택한 탄탈 커패시터는 TAJA106K016RNJ 커패시터로 주요 스펙은 10uF, 내압 16V, CASE-A-3216-18(mm) 패키지이다. JLCPCB 파트번호는 C7171이다.

https://jlcpcb.com/partdetail/-TAJA106K016RNJ/C7171

TAJA106K016RNJ | -- | Tantalum Capacitors | JLCPCB

One-Stop Turnkey PCBA & Free Asembly for Your PCBs Get $30 New User Coupons & Monthly $24 PCBA Coupons

jlcpcb.com

추가적으로 고주파 특성을 위해 0.1uF MLCC 커패시터도 추가해주었다.

2. EN 신호

데이터 시트에 따르면 VIL은 0.4V이고 VIH는 1.2V라는 것을 알 수 있다. 또한 VEN은 5.5V일 때 IEN은 5.5uA 역시 알 수 있다. 또한 앞선 OR 회로 설계에 따르면 LDO Regulator에 입력되는 전압의 크기는 4.65V 정도이다. LDO Regulator의 내부 블록 다이어 그램은 다음과 같이 생겼다.

LDO Regulator는 항상 킨 상태이므로 Push-pull 회로를 이용하여 전압을 높은 상태로 유지해주기로 한다. 과전류 보호를 위해서 1KΩ의 저항을 달아주기로 한다. 해당 저항을 사용할 경우 (VIN - VIH)/R = (4.65 - 1.2)/1K = 3.45*10^(-3)으로 5.5uA보다 크므로 동작에 문제가 없다.

3. 출력 커패시터

1uF 이상의 커패시터를 달아주는 것을 권장하고 있다. 데이터시트에 의하면 권장 ESR은 5mΩ ~ 500mΩ이고, output 커패시터 용량은 0.7uF ~ 10uF로 정의되고 있다. 3.3uF 용량의 커패시터를 선정하였다. 저항과 커패시터 선정 방법에 대해서는 다른 글에서 따로 다루겠다.

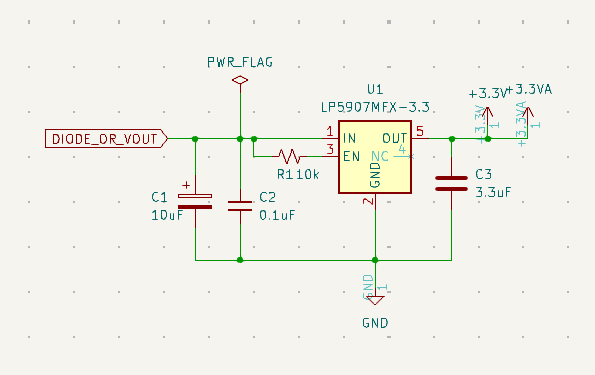

최종적으로 회로도는 다음과 같이 작성하였다.

이 것으로 이번 글을 마친다. 다음 글에서는 커패시터 소자와 저항 소자에 대해서 다루겠다. (수십개에 달하는 저항 소자와 커패시터 소자의 선정 이유를 설명하는 것은 번거로운 일이다!)